## **———** МОДЕЛИРОВАНИЕ ———

УЛК 621.382.323

# МОДЕЛИРОВАНИЕ КРЕМНИЕВЫХ ПОЛЕВЫХ С ПОЛНОСТЬЮ ОХВАТЫВАЮЩИМ ЗАТВОРОМ НАНОТРАНЗИСТОРОВ С ВЫСОКИМ k ПОДЗАТВОРНОГО ДИЭЛЕКТРИКА

© 2023 г. Н. В. Масальский\*

Федеральное государственное учреждение Федеральный научный центр Научно-исследовательский институт системных исследований РАН, Москва, Россия \*E-mail: volkov@niisi.ras.ru

> Поступила в редакцию 06.02.2023 г. После доработки 01.03.2023 г. Принята к публикации 02.03.2023 г.

Обсуждаются электрофизические характеристики кремниевого цилиндрического с полностью охватывающим затвором полевого нанотранзистора с диэлектриками подзатворного окисла  ${\rm Al_2O_3}$  и  ${\rm HfO_2}$ . Результаты численного моделирования показывают, что использование диэлектриков с высоким k оказывает заметное влияние на все основные характеристики транзистора по сравнению с оксидом кремния. Из полученных данных следует, что при масштабировании степень деградации электро-физических характеристик транзистора коррелирует с уровнем k — она снижается с ростом k. Это связываем с тем, что уменьшение влияния затвора на характеристики транзисторной структуры, особенно в подпороговой области, частично компенсируется использованием диэлектриков с высоким k.

Kлючевые слова: кремневая цилиндрическая нанотранзисторная архитектура, полностью охватывающий затвор, диэлектрик с высоким k, моделирование

DOI: 10.31857/S0544126923700278, EDN: UBVMOR

# 1. ВВЕДЕНИЕ

Диэлектрические материалы затвора кремниевого полевого транзистора сыграли значительную роль в разработке современных наноразмерных электронных устройств с высокими эксплуатационными характеристиками [1, 2]. Материалы с высокой диэлектрической проницаемостью (с высоким k) являются более подходящими, чем традиционный оксид кремния SiO2, из-за меньшей требуемой толщины пленки подзатворного диэлектрика  $(t_{ox})$ , что приводит к снижению пороговое напряжения и улучшению подпороговой характеристики полевого транзистора [1, 3, 4]. Хотя неуклонное масштабирование транзисторов может увеличить степень интеграции и производительность СБИС [1, 2, 5, 6], но проявление коротко-канальных эффектов (ККЭ) и деградация транзисторных электро-физических характеристик являются нежелательными последствиями масштабирования. Поскольку, в результате масштабирования, толщина  $t_{ox}$  достигает менее одного нанометра для повышения электрических характеристик устройства, то проблема роста тока утечки затвора из-за квантового туннелирования усиливается [4, 5]. Поэтому необходимо заменить обычный изолятор  $SiO_2$  материалом с высоким k, чтобы увеличить эффективную толщину подзатворного оксида для сохранения превосходных электрических характеристик [5, 7-9].

В кремниевом полевом транзисторе с полностью охватывающим затвором из-за того, что затвор окружает весь объем рабочей области, электростатический контроль затвора над ней выше по сравнению с другими структурами, что предоставляет возможность дополнительно улучшить электро-физические характеристики транзистора [5, 6, 101. Таким образом, данная транзисторная концепция является основным кандидатом с максимальной способностью расширить закон Мура в область ультра нанометровых топологических норм. Однако основная проблема обсуждаемого класса транзисторов — высокий ток утечки ( $I_{\rm off}$ ) и высокий подпороговый наклон (SS), вызванная масштабированием, что ограничивает производительность устройств для приложений с низким энергопотреблением и высокой тактовой частотой [8, 9].

Цель данной работы является оценка электрофизических характеристик тонких кремниевых с полностью охватывающим затвором полевых транзисторов, длины каналов которых находятся в декананометровом диапазоне, с материалами подзатворного оксида с высоким значением диэлектрической проницаемости: диоксид гафния (HfO<sub>2</sub>,

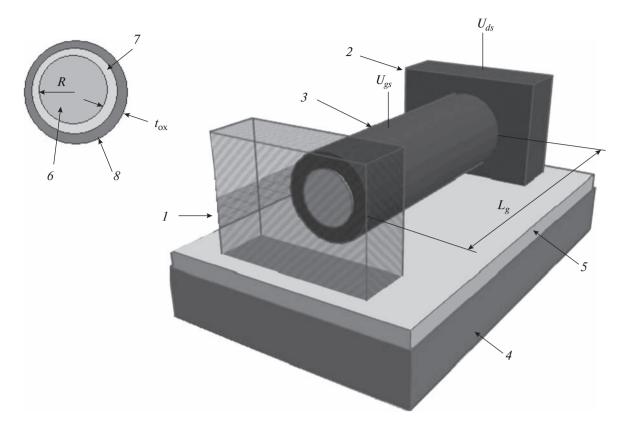

**Рис. 1.** Структурная схема транзистора, где I — исток, 2 — сток, 3 — рабочая область, 4 — кремниевая подложка, 5 — пленка оксида кремния, 6 — кремниевая сердцевина рабочей области, 7 — пленка оксила кремния, 8 — пленка диэлектрика с высоким k,  $L_g$  — длина рабочей области, R — радиус кремниевой сердцевины рабочей области.

$\kappa = 25$ ) и оксид алюминия (Al<sub>2</sub>O<sub>3</sub>,  $\kappa = 9.3$ ) [11]. Для этого мы используем симулятор, основанный на подходе моделирования, который подробно изложен в [12]. Он основан на упрощении модели рассеяния, используя приближение времени релаксации [13]. Линеаризация по времени релаксации позволяет получить прямое решение 1D транспортного уравнения Больцмана (ТУБ) эффективным способом. Применяемый подход включает все существенные особенности квазибаллистического переноса в декананометровом масштабе [4]. Затем мы численно исследуем электро-физические характеристики масштабируемых нанотранзисторов вплоть до длины канала 11 нм. Реализация такой процедуры весьма эффективна для формирования элементной базы для перспективных интегральных микросхем. Следует отметить, что поскольку поверхность Si-SiO2 имеет лучшее качество в процессе изготовления [14, 15], диэлектрик затвора для всех исследуемых прототипов состоит из двух слоев: тонкий SiO<sub>2</sub> на рабочей области и диэлектрика с высоким k поверх пленки SiO<sub>2</sub>. Мы откалибровали симулятор при помощи 3D моделирования, выполняемого посредством лицензионной системы приборно-технологического моделирования TCAD Sentaurus [16], модели, кото-

рого были настроены с учетом экспериментальных данных для оксида кремния (SiO<sub>2</sub>,  $\kappa$  = 3.9) [14].

# 2. ПАРАМЕТРЫ ТРАНЗИСТОРА И НАСТРОЙКА МОДЕЛИРОВАНИЯ

Рис. 1 иллюстрирует трехмерное представление анализируемой приборной структуры. Она включает исток (поз. I), сток (поз. 2) и рабочую область (поз. 3), где  $L_{\rm g}$  — длина рабочей области и длина затвора транзистора. Границы примыкания рабочей области к истоку/стоку являются резкими. Нет перекрытия между затвором и областями истока и стока. На вставке показало поперечное сечение рабочей области. Ее кремниевая сердцевина (поз. 6) полностью охвачена пленкой оксида кремния толщиной 0.5 нм (поз. 7), и поверх ее окружает пленка диэлектрика с высоким kтолщиной 1 нм (поз. 8). Это связано с лучшим соответствием и качеством интерфейса Si-SiO<sub>2</sub>, который образуется в процессе изготовления. Транзисторная структура помещена подложку КНИ (кремний на изоляторе).

Для расчета электрических характеристик рассматриваемого устройства используется квази трехмерное моделирование. Оно базируется на допуще-

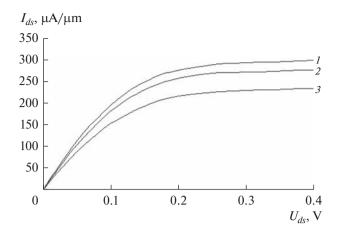

**Рис. 2.** ВАХ  $I_{ds}(U_{ds})$  при  $U_{gs}=0.4$  В для разных k, где  $1-k=25,\,2-k=9,\,3-k=3.9.$

нии, что транспорт носителей в наноразмерном транзисторе совершается через одномерные поддиапазоны общей энергетической зоны проводимости. Это следует из того, что волновые функции каждого поддиапазона ограничены поперечным сечением прибора [17, 18]. Для не совсем ультра тонких структур можно моделировать транспорт носителей при нормальных условиях, используя квазиклассическое мульти зонное уравнение переноса Больцмана [19]. В этом случае квазиклассические модели, основанные на 1D мульти зонном ТУБ, позволяют получить достоверные электро-физические характеристики, когда уравнение Больцмана решается самосогласованно с 3D уравнением Пуассона и 2D уравнением Шредингера для получения самосогласованных потенциалов и энергий поддиапазонов и волновых функций. Квазианалитическое решение 3D уравнения Пуассона на основе метода разделения переменных подробно рассмотрено [20]. Там же показано, что такой подход практические не снижает точность решения относительно прямых численных методов вычисления потенциала. Метод разделения переменных положен в основу решения 2D уравнения Шредингера, которое детально представлено в [21], и там же сделаны оценки погрешности вычисления волновых функций. Следует отметить, что в отличии от ультра коротких транзисторных структур где рассеяние фононов и туннелирование от истока к стоку довольно значительны, по мере увеличения длины рабочей области их влияние становится менее значимым, а длинах рабочей области более 10 нм не существенными [22]. Поэтому, и квантовые явления переноса представляются незначительными, а использование ТУБ является вполне обоснованным.

Компьютерное моделирование выполнено для транзисторных структур с различными технологическими параметрами. В расчетах длина рабочей

области  $L_g$  изменяется в диапазоне 11-25 нм, радиус R фиксирован и равен 3 нм. Фиксированы размеры стока/истока, длина которых составляла 25 нм, ширина и высота составляют 50 нм. Они равномерно легированы с концентрацией  $0.5 \times 10^{21}$  см $^{-3}$ . Кремниевая рабочая область полагается нелегированной с собственной концентрацией носителей  $1 \times 10^{13}$  см $^{-3}$ . В расчетах учитывается для зоны проводимости три пары вырожденных долин с анизотропной эффективной массой и проникновение волновой функции в подзатворный диэлектрик, который обеспечивает высоту потенциального барьера более 3 эВ. Температура решетки постоянна и равна 300 К.

### 3. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ

На рис. 2 приведены результаты численного моделирования ВАХ  $I_{ds}(U_{ds})$  при  $U_{gs}=0.4$  В реперной транзисторной структуры ( $L_g=25$  нм) с тремя различными материалами верхней пленки подзатворного диэлектрика. Отметим, заметный рост тока стока связанный с использованием в подзатворном окисле материала с высокой диэлектрической проницаемостью совпадает с общей тенденцией характерной для всех типов кремниевых полевых транзисторов [5, 6, 22].

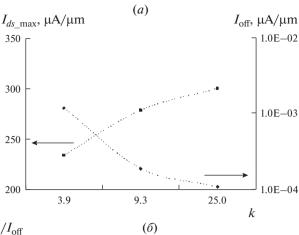

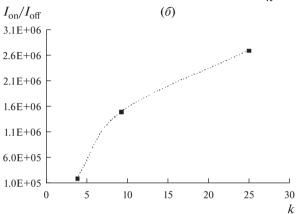

На рис. З показаны извлеченные из результатов моделирования зависимости  $I_{ds\_max(k)}$ ,  $I_{off(k)}$  и отношения  $I_{on}/I_{off(k)}$ . Из приведенных данных прослеживается общая тенденция улучшения характеристик с увеличением диэлектрической проницаемости. Очевидно, что наилучшие результаты получаются, когда оксид гафния используется в качестве подзатворного диэлектрика.

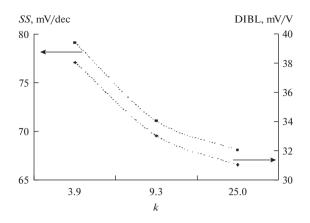

Экстрагированные из результатов моделирования зависимости подпорогового наклона и DIBL-эффекта приведены ниже на рис. 4. Обе эти зависимости проявляю практически одинаковую тенденцию к снижению с ростом k. Согласно этим данным, по мере увеличения диэлектрической проницаемости подзатворного оксида ток стока увеличивается, а подпороговый наклон уменьшается. Поэтому кремниевый полевой транзистор с полностью охватывающим затвором с подзатворным диэлектриком HfO<sub>2</sub> представляется наиболее интересным для цифровых приложений [6]. Это свойство обусловлено самой высокой электростатической управляемостью затвора рабочей областью, который сверх интенсивно управляет всеми носителями находящимися в рабочей области и обеспечивает их акцентированный перенос от истока к стоку.

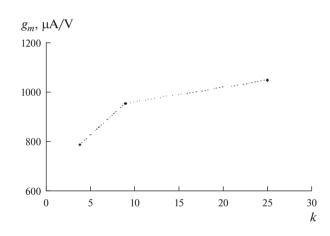

Проводимость транзистора  $(g_m)$ , показывает, насколько сильно напряжение затвора влияет на ток стока, и определяется следующим соотношени-

**Рис. 3.** Зависимости (a)  $I_{ds\_max}(k)$  при  $U_{ds}=U_{gs}=0.4$  и  $I_{\rm off}(k)$  при  $U_{ds}=0.4$  В и  $U_{gs}=0.0$  В, (б)  $I_{\rm on}/I_{\rm off}(k)$ . Здесь и ниже на рисунках жирными маркерами отмечены значения параметра для рассматриваемых диэлектриков. Пунктирной линией показано гипотетическое поведение параметра.

ем:

$$g_m = \frac{dI_{ds}}{dU_{gs}} \Big|_{U_{ds}-{

m const}}$$

. Параметр  $g_m$  является важной

характеристикой и определяет эффективность усиления сигнала. На рис. 5 показано изменение  $g_m$  реперного прототипа в открытом режиме ( $U_{ds}=0.4~\mathrm{B}$ ) с различными диэлектриками подзатворного оксида. В данном случае проводимость увеличивается с увеличением значения диэлектрической проницаемости. Обобщая все полученные данные, можно сделать вывод, что подвижность носителей в рабочей области реперного прототипа выше при использовании материала с высоким k, что снижает паразитное сопротивление и сопротивление включения.

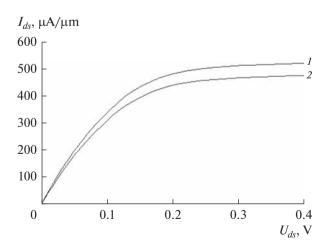

Результаты численного масштабирования длины  $L_g$  до 11 нм для прототипов с разными подзатворными оксидами приведены на рис. 6. Для них ВАХ рассчитаны только для материалов с высоким k. Из-за сильного влияния ККЭ прототип с

**Рис. 4.** Зависимости SS(k) и DIBL(k).

**Рис. 5.** Зависимость  $g_m(k)$ .

**Рис. 6.** ВАХ  $I_{ds}(U_{ds})$  при  $U_{gs}=0.4$  В для разных k, где  $1-k=25,\,2-k=9.$

| k    | $I_{ds\_{ m max}}$ , мкА/мкм | <i>SS</i> , мВ/дес | $I_{ m off}$ , мк $A$ /мкм | $I_{ m on}/I_{ m off}$ | $g_m$ , мк $A/B$ | $g_m/I_{ds}$ , 1/B |

|------|------------------------------|--------------------|----------------------------|------------------------|------------------|--------------------|

| 9.3  | 479.1                        | 65                 | 0.004                      | $1.2 \times 10^{5}$    | 1772             | 3.6                |

| 25.0 | 525.4                        | 62                 | 0.0023                     | $2.25 \times 10^{5}$   | 1962             | 3.7                |

Таблица 1. Основные электро-физические характеристики

подзатворным диэлектриком только из оксида кремния не рассматривался.

Анализировались те же характеристики, что и для реперной структуры. Полученные данные приведены в табл. 1. Отметим, примерно 75% увеличение тока стока, практически двукратный рост проводимости и небольшое снижение параметра SS. Существенно деградировали, практически на порядок ток  $I_{\rm off}$  и отношение  $I_{\rm on}/I_{\rm off}$ .

Другой важный параметр  $g_m/I_{ds}$  — эффективность проводимости представляет собой способность устройства усиливать сигнал при определеной рассеиваемой мощности и оценивает эффективность устройства для преобразования мощности постоянного тока в частоту переменного тока [23]. Исходя из полученных данных, следует, что по мере роста к соотношение  $g_m/I_{ds\_max}$  будет возрастать резче при более низких напряжениях  $U_{gs}$ , и это связано с лучшим поведением подпороговой области.

Из полученных данных следует, что степень деградации электро-физических характеристик прототипа с более низкой диэлектрической проницаемостью больше. Это связано с тем фактом, что при масштабировании влияние затвора на характеристики транзисторной структуры, особенно в подпороговой области, уменьшается, что может быть частично компенсировано использованием диэлектриков с высоким k.

#### **ЗАКЛЮЧЕНИЕ**

Численно проанализированы электрофизические характеристики кремниевого цилиндрического с полностью охватывающим затвором полевого нанотранзистора с диэлектриками подзатворного окисла  $Al_2O_3$  и  $HfO_2$ . Результаты численного моделирования показывают, что использование диэлектриков с высоким k оказывает заметное влияние на все основные характеристики транзистора по сравнению с традиционным оксидом кремния. Из полученных данных следует, что при масштабировании существенно деградировали, практически на порядок ток  $I_{\text{off}}$  и отношение  $I_{\text{on}}/I_{\text{off}}$ . Степень деградации электро-физических характеристик транзистора коррелирует с уровнем k: с ростом k снижается степень деградации. Это связываем с тем, что влияние затвора на характеристики транзисторной структуры, особенно в подпороговой области, уменьшается, что может быть частично компенсировано использованием диэлектриков с высоким k. Другие важные характеристики заметно улучшились. Использование диэлектрика с высоким k в подзатворном оксиде может существенно повысить электро-физические характеристики кремниевого цилиндрического с полностью охватывающим затвором полевого нанотранзистора так, чтобы удовлетворить требованиям закона Мура.

#### БЛАГОДАРНОСТИ

Публикация выполнена в рамках государственного задания ФГУ ФНЦ НИИСИ РАН "Проведение фундаментальных научных исследований (47 ГП)" по теме № FNEF-2022-0022 "Математическое обеспечение и инструментальные средства для моделирования, проектирования и разработки элементов сложных технических систем, программных комплексов и телекоммуникационных сетей в различных проблемно-ориентированных областях".

#### СПИСОК ЛИТЕРАТУРЫ

- 1. Ferain I., Colinge C.A., Colinge J. Multigate transistors as the future of classical metal—oxide—semiconductor field-effect transistors // Nature. 2011. V. 479. P. 310—316.

- 2. *Taur Y.*, *Ning T.H.* Fundamentals of modern VLSI devices // Cambridge university press. 2013.

- 3. *Karbalaei M., Dideban D.* A novel silicon on insulator MOSFET with an embedded heat pass path and source side channel doping // Superlattices and Microstructures. 2016. V. 90. P. 53–67.

- 4. *Anvarifard M.K., Orouji A.A.* Proper electrostatic modulation of electric field in a reliable nano-SOI with a developed channel // IEEE Transactions on Electron Devices. 2018, V. 65. P. 1653–1657.

- 5. *Tomar G., Barwari A.* Fundamental of electronic devices and circuits // Springer. 2019.

- International Technology Roadmap for Semiconductors (ITRS) Interconnect, 2020 Edition. [Online] Available: https://irds.ieee.org/editions/2020

- 7. *Karbalaei M., Dideban D.* A scheme for silicon on insulator field effect transistor with improved performance using graphene // ECS Journal of Solid State Science and Technology. 2019. V. 8. P. M85–M92.

- Shaker A., El-Sabbagh M., El-Banna M.M. Influence of drain doping engineering on the ambipolar conduction and high-frequency performance of TFETs // IEEE Transactions on Electron Devices. 2017. V. 64. P. 3541– 3547

- 9. Nagy D., Indalecio G., Garcia-Loureiro A.J., Elmessary M.A., Kalna K., Seoane N. FinFET versus gateall-around nanowire FET: performance, scaling, and

- variability // IEEE Journal of the Electron Devices Society, 2018. V. 6. P. 332–40.

- Narang R., Saxena M., Gupta R.S., Gupta M. Drain current model for a gate all around (GAA) p-n-p-n tunnel FET // Microelectronics Journal. 2013. V. 44(6). P. 479–488.

- Baklanov M., Green M., Maex K. Dielectric Films for Advanced Microelectronics. // John Wiley and Sons, LTD. 2007.

- 12. *Масальский Н.В.* Моделирование ВАХ ультра тонких КНИ КМОП нанотранзисторов с полностью охватывающим затвором // Микроэлектроника. 2021. Т. 60. № 6. С. 387—393.

- 13. *Jin S.*, *Park Y.J.*, *Min H.S.* A three-dimensional simulation of quantum transport in silicon nanowire transistor in the presence of electron-phonon interactions // J. Appl. Phys. 2006. V. 99. P. 123719-1—123719-10.

- 14. Elmessary M.A., Nagy D., Aldegunde M., Seoane N., Indalecio G., Lindberg J. Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations // Solid-State Electronics. 2017. V. 128. P. 17—24.

- Bousari N.B., Anvarifard M.K., Haji-Nasiri S. Improving the electrical characteristics of nanoscale triple-gate junctionless FinFET using gate oxide engineering // AEU -International Journal of Electronics and Communications. 2019. V. 108. P. 226–34.

- TCAD Sentaurus; Synopsys Inc.: Mountain View, CA, USA, 2017.

- 17. *Moon D., Choi S., Duarte J., Chio Y.* Investigation of silicon nanowire gate all-around junction less transistors built on a bulk substrate // IEEE Trans Electron Devices. 2013. V. 60. P. 1355–1360.

- 18. Avilla-Herrerea F., Paz B., Cerdeira A., Estrada M., Pavanello M. Charge-based compact analytical model for junction less triple-gate nanowire transistors // Solid-State Electronics. 2016. V. 121. P. 23–27.

- 19. *Briggs S., Leburton J.P.* Size effects in multisubband quantum wire structures // Phys. Rev. B. 1988. V. 38. P. 8163–8170.

- Mani Manoj P., Pandey K. Surface potential and threshold voltage model of fully depleted narrow channel SOI MOSFET using analytical solution of 3D Poisson's equation // J. of nano- and electronic physics. 2015. V. 7. P. 2002–2007.

- Orlikovsky A., Vyurkov V., Lukichev V., Semenikhin I., Khomyakov A. All quantum simulation of ultrathin SOI MOSFET in nanoscale semiconductor-on-insulator structures and devices // Springer. 2007.

- 22. Nanoelectronics: Devices, Circuits and Systems // Editor by Brajesh Kumar Kaushik. Elsevier. 2018.

- 23. *Tayal S., Nandi A.* Analog/RF performance analysis of inner gate engineered junctionless Si nanotube // Superlattices Microstruct. 2017. V. 111. P. 862–871.